アナログ回路技術を駆使して、社会に役立つ無線ハードウェアの開発に取り組んでいます。

## 略歴

2012年までの27年間、日本電信電話株式会社先端技術総合研究所において半導体プロセスインテグレーションおよびアナログ集積回路設計の研究に従事した。その後、日本工業大学電気電子通信工学科の教授に着任し、現在は無線端末用のハードウェアおよび回路設計を中心とした研究に着手している。

## 研究紹介

## 多相アナログ信号による高性能回路の研究

また発振回路に多相信号による位相補償技術を適用して、信号遅延の悪影響を打ち消し、発振信号の純度を高める研究なども行っています。低成本の高機能LSI等に関する成果が期待できます。

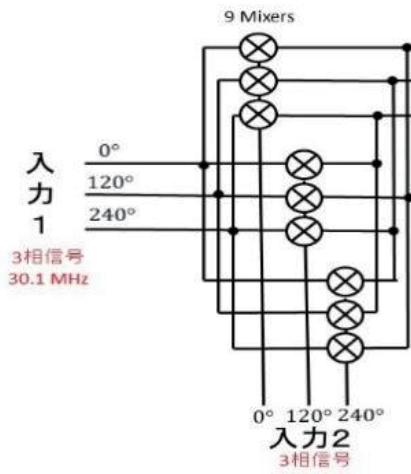

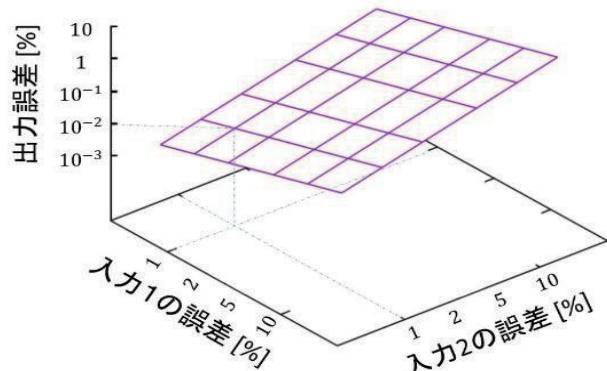

N相 ( $N \geq 3$ ) のアナログ信号を用いることにより集積回路の信号処理精度や動作速度の向上させる研究を行っています。例えば通常の周波数変換回路 (Mixer: 掛算回路) を  $N^2$  個組み合わせることで、出力に含まれる相対誤差の大きさを2入力の相対誤差の積の大きさにする周波数変換回路を考案しました。これは下図に示されるように、2入力に含まれる誤差がともに 1 % の場合、出力に含まれる相対誤差は 0.01 % となり、誤差を激減できます。

## 共同研究の事例

- 回路基板の雑音指數評価

- 低電圧動作周波数変換回路の開発

- 多相発振回路の開発、など

## 主な論文発表

- 1) M. Ugajinほか: A study of phase-adjusting architectures for low-phase-noise quadrature voltage-controlled oscillators, IEICE Trans. on Electron., Vol.E106-C (2023), 59-66.

- 2) M. Ugajin(ほか): An  $(N + N^2)$ -Mixer Architecture for a High-Image-Rejection Wireless Receiver with an  $N$ -Phase Active Complex Filter, IEICE Trans. on Fundamentals, Vol.E100-A (2017), 1008-1014.